## Micro & Nano Fabrication techniques

Dominique Mailly Centre de Nanosciences et de Nanotechnologie CNRS - Marcoussis

#### Ouline of the lecture

- Introduction to nanofabrication techniques and microelectronics

- Lithography techniques:

- Optical lithography

- Lithography using focused beams:

- Electron beam lithography

- Ion beam lithography

- Near field techniques

- Imprint techniques

- Metal and dielectric deposition techniques:

- Thermal evaporation

- Chemical vapor deposition

- Atomic layer deposition

- Transfer techniques

PARIS

universite

- Chemical wet etching

- Ion beam etching

- Reactive ion beam etching

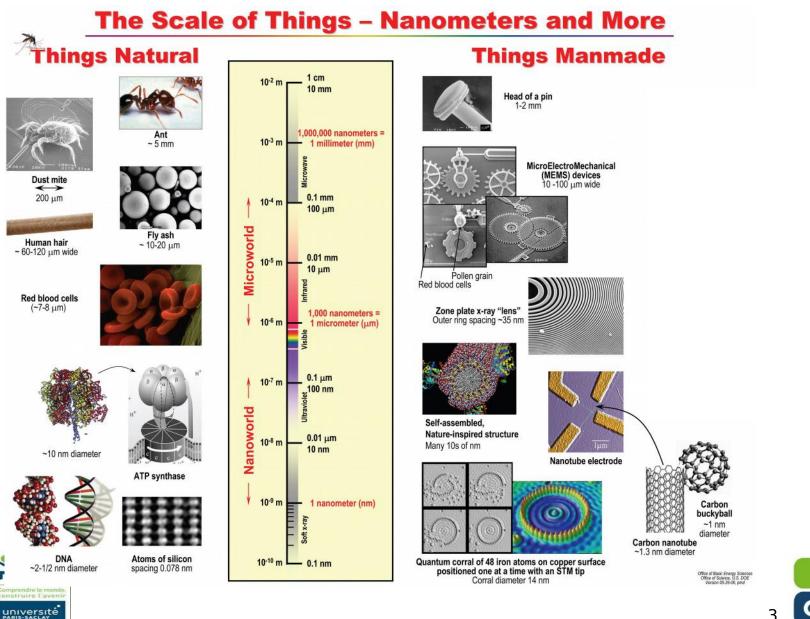

#### Introduction:length scales

CIS

3 C2N

## Micro and nanofabrication

- Microfabrication is the process of fabricating structures from few decade of micrometer down to a tenth of micrometer

- Nanofabrication is the process of fabricating structures of size below 100nm.

- There is some debate to set how many space direction need to be taylored.

- Usually if only one direction is involved (2d-film) this is not really considers as nanofabrication (spill oil on water..)

- The microelectronics industry has continously pushed Micro & Nanofab performance since the 60's

## **Historical review of microelectronics**

- 1947 : first transistor (Bardeen, Brattain, Shockley, Nobel price 1956)

- 1957: first use of photolithography

- 1959: first integrated circuits (→ Nobel 2000 for Noyce and Kilby)

http://www.nobel.se/physics/educational/transistor/function/index.html

The first transistor

Today's transistor

COMPARISE COMPARISE Company of the tempore construire l'aventre université

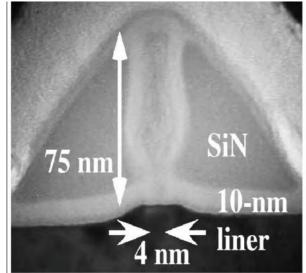

nm functional transistors are below 10nm

Nowdays the length of the

gate of the

smallest

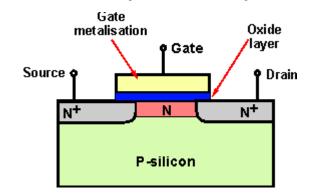

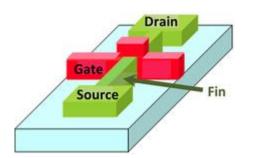

#### MOSFET

# <u>Metal Oxyde semiconductor Field Effect Transistor</u> <u>(MOSFET)</u>

Either:

$\rightarrow$ voltage controled switch

$\rightarrow$ signal amplifier

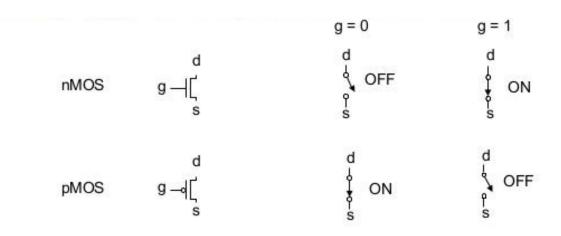

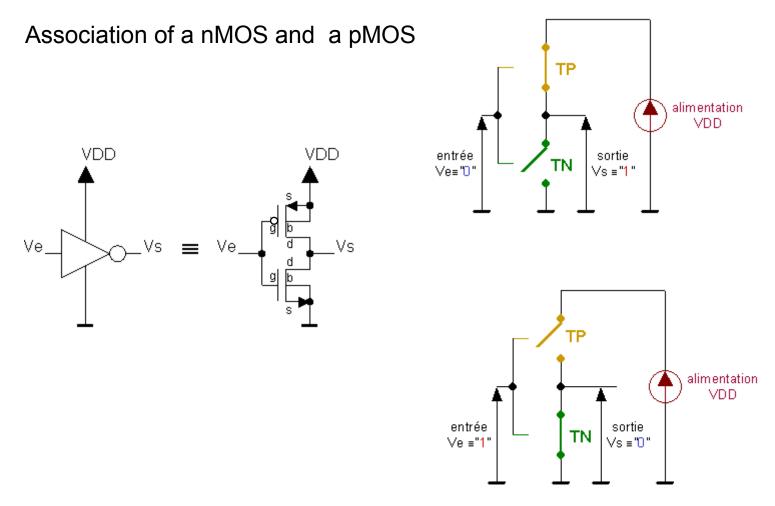

### CMOS = complementary MOS

No current is flowing in the static regime

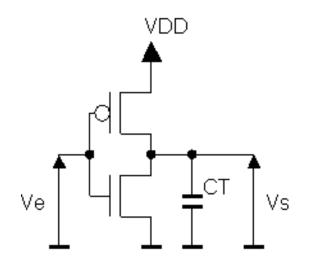

## **CMOS** inverteur

- During the switch of Ve the source bring the energy needed to discharge the equivalent capacitor CT of the circuit.

- This abscence of dissipation in the static regime allowed the drastic increase of transistor in the IC's since 1970.

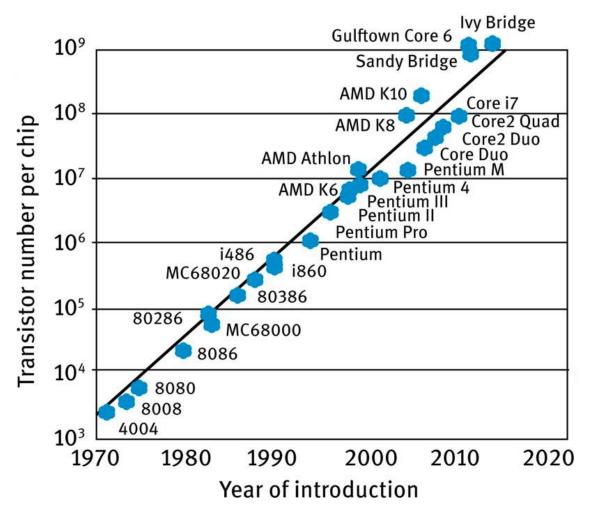

## Transistor number per chip : the Moore's law

Gordon Moore

The number of transistor double every 18 months

#### Moore's law

#### Moore and technology roadmap (ITRS)

|    | Year of Production                                                | 2013     | 2015     | 2017     | 2019     | 2021     |

|----|-------------------------------------------------------------------|----------|----------|----------|----------|----------|

| 1  | Logic Industry "Node Name" Label                                  | 16/14    | 10       | 7        | 5        | 3.5      |

| 2  | Logic ½ Pitch (nm)                                                | 40       | 32       | 25       | 20       | 16       |

| 3  | FinFET Fin Half-pitch (new) (nm)                                  | 30       | 24       | 19       | 15       | 12       |

| 4  | FinFET Fin Width (new) (nm)                                       | 7.6      | 7.2      | 6.8      | 6.4      | 6.1      |

| 5  | FinFET Fin Width (nm) (Detailed )                                 | 6.4      | 5.3      | 4.4      | 3.7      | 3.1      |

| 6  | 6-t SRAM Cell Size(um2) [@60f2]                                   | 0.096    | 0.061    | 0.038    | 0.024    | 0.015    |

| 7  | MPU/ASIC HighPerf 4t NAND Gate<br>Size(um2)                       | 0.248    | 0.157    | 0.099    | 0.062    | 0.039    |

| 8  | 4-input NAND Gate Density<br>(Kgates/mm) [@155f2]                 | 4.03E+03 | 6.37E+03 | 1.01E+04 | 1.61E+04 | 2.55E+04 |

| 9  | 450mm Production High Volume<br>Manufacturing Begins (100Kwspm)   |          |          | 2018     |          |          |

| 10 | Vdd (High Performance, high Vdd<br>transistors)[**]               | 0.86     | 0.83     | 0.8      | 0.77     | 0.74     |

| 11 | 1/(CV/I ) (1/psec) [**]                                           | 1.13     | 1.53     | 1.75     | 1.97     | 2.1      |

| 12 | On-chip local clock MPU HP [at 4%<br>CAGR] (GHz)                  | 5.5      | 5.95     | 6.44     | 6.96     | 7.53     |

| 13 | Maximum number wiring levels<br>[unchanged]                       | 13       | 13       | 14       | 14       | 15       |

| 14 | MPU High-Performance (HP) Printed<br>Gate Length (GLpr) (nm) [**] | 28       | 22       | 18       | 14       | 11       |

| 15 | MPU High-Performance Physical<br>Gate Length (GLph) (nm) [**]     | 20       | 17       | 14       | 12       | 10       |

| 16 | ASIC/Low Standby Power (LP)<br>Physical Gate Length (nm)          | 23       | 19       | 16       | 13       | 11       |

© CEA 2006. Tous droits réservés.

637 un altream altrea milicolinities una attream team munch ao an unation un inclinente un nechaux sua funcio a au no milicolini un de contra dura

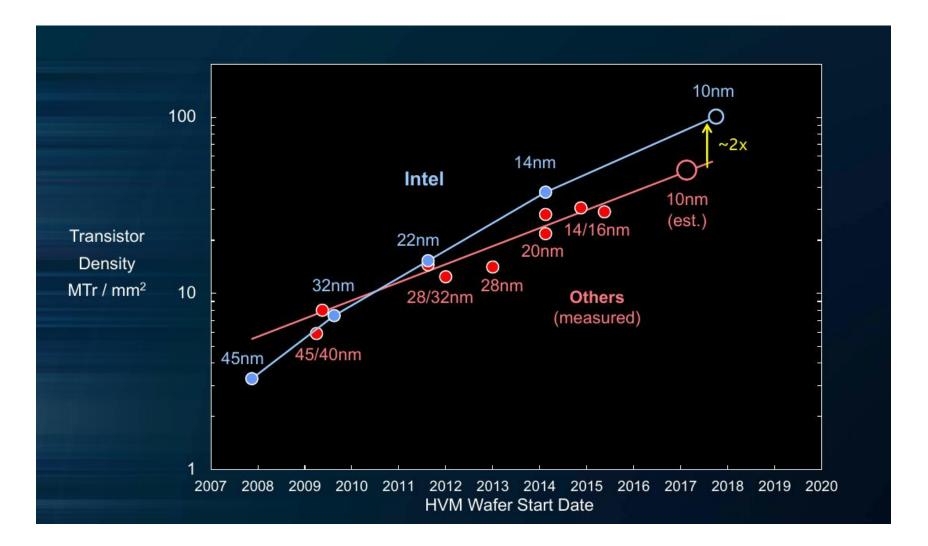

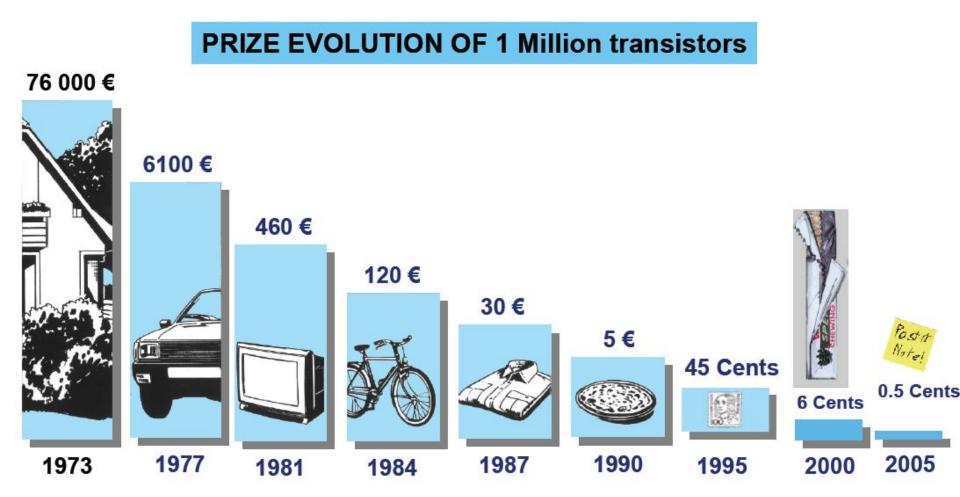

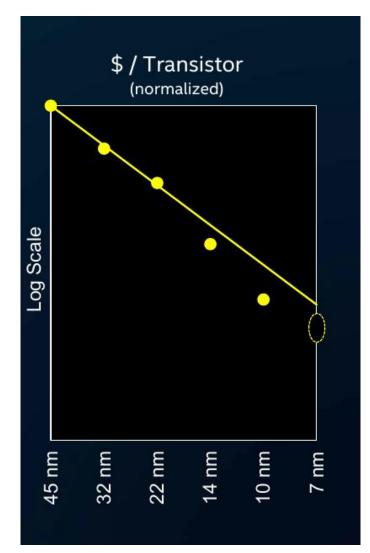

Despite a strong increase of the complexity of the technology the price of a transistor still decreases due to the increase of density of transistors per chip.

This constant evolution is possible because one uses a massive parallel fabrication process.

Impressive progress of optical lithography

For long time one believes that one can only reproduce features of the size of the wavelength that one uses. Resolution was limited to few hundred of nanometers

Currently the minimum size in an IC can be less then10nm !

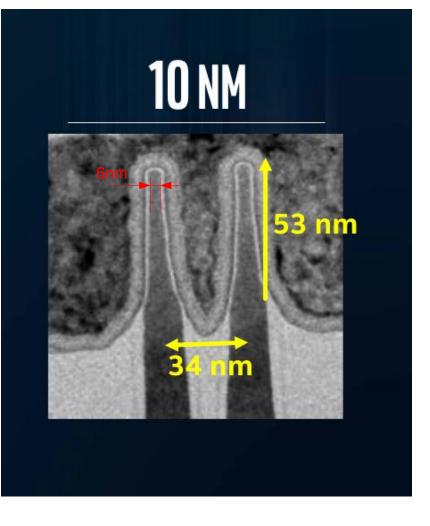

#### Size of the Intel double fin-FET of the 10nm node (2017)

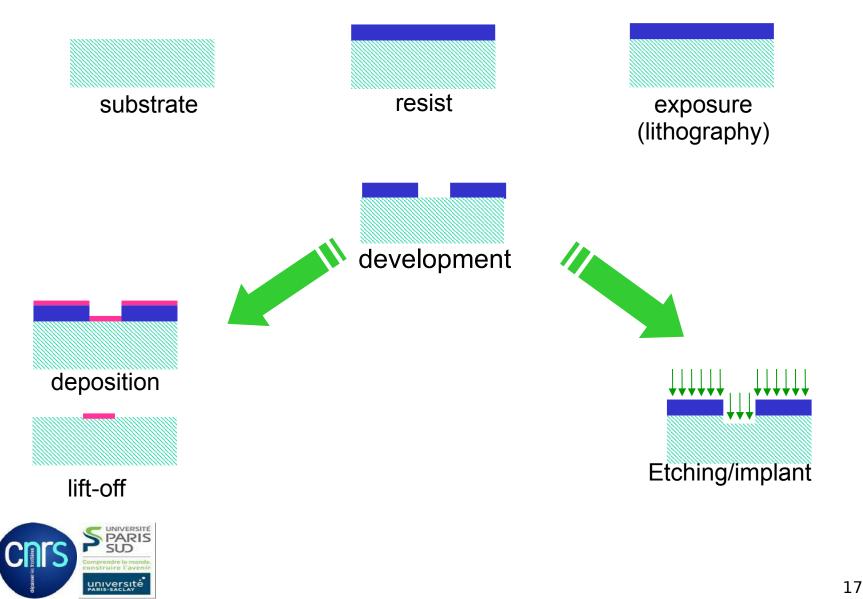

# What are the main step of micro/nano fab

One needs to define a selected area where we can :

- Implant

- Deposit material

- Etch

The technique allowing to select a well defined area is called lithography

#### **Typical process**

## lithography

#### This is the crucial step that will define the size

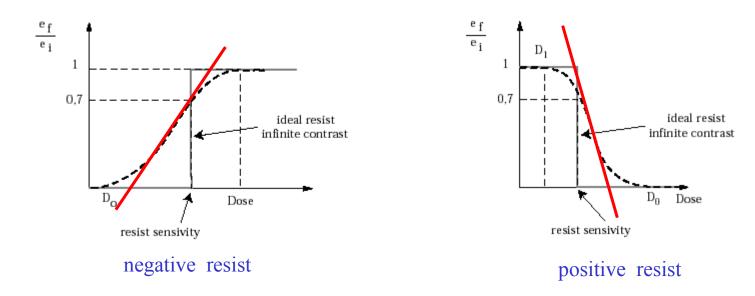

#### **Resist and contrast**

Most of the time we don't want a nice gray scale but a very contrasted result.

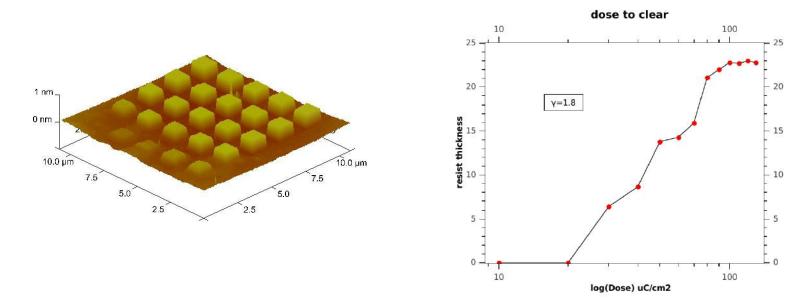

#### Measurement of the contrast

One exposes aereas with increasing doses and measure the remaining height after development

Contrast curves strongly depend on the process : dose + developper + temperature (developper)

**Optical lithography resists**

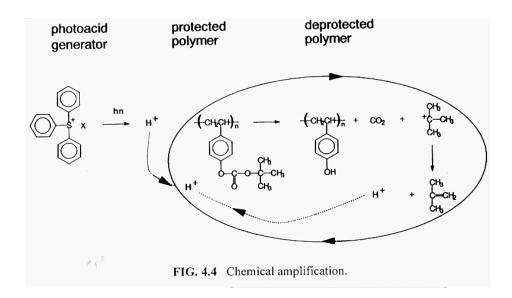

- Chemically amplified resist for a high sensitivity

- catalyst acid is produced by the photon

- Activated reaction: hydrolyse (positive resist), crosslink (negative resist)

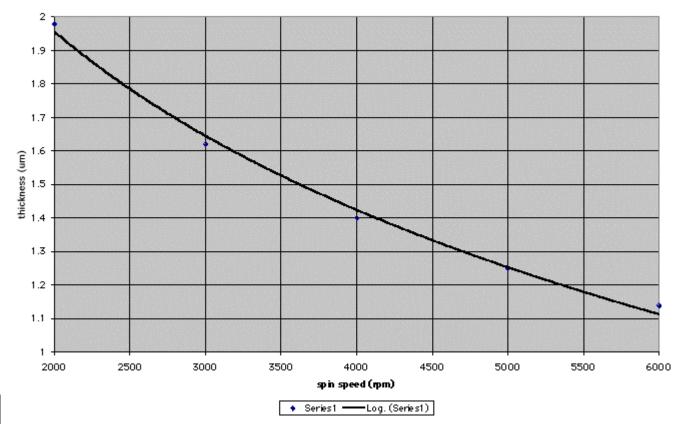

## Spinning tool

To obtain a controlled flat film of resist one uses the centrifugal force

### **Resist spinning**

spin curve AZ 5214 source Clariant/Mattern

### **Resist thickness**

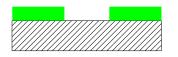

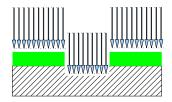

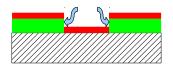

Resist profile after litho+ development

Etching : depends on the differential rate of etching between resist and material

Metal deposition : lift off

resist thickness ~3 x metal thickness

To have a safe solvent penetration

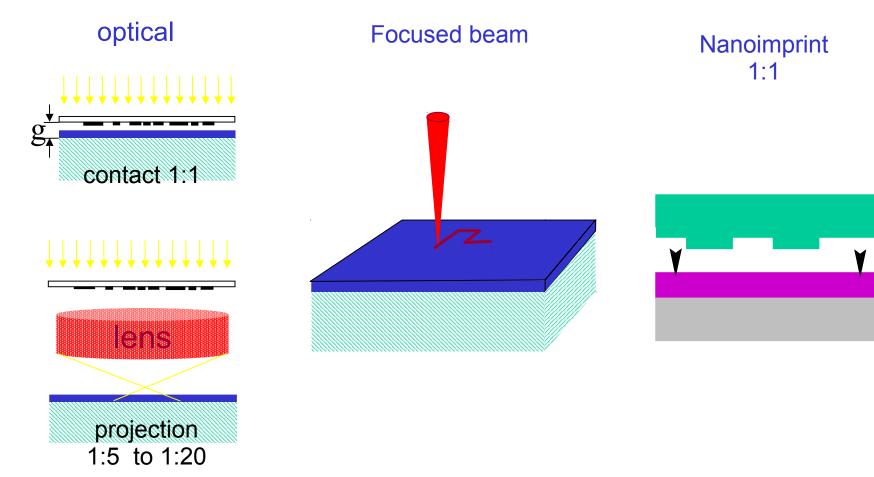

# **Optical lithography**

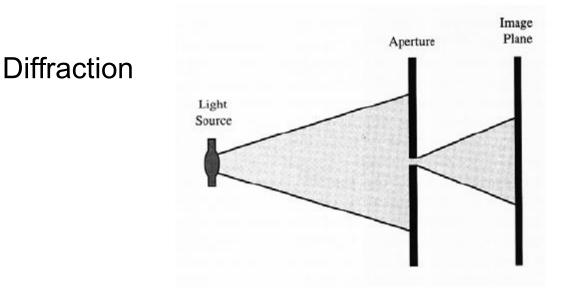

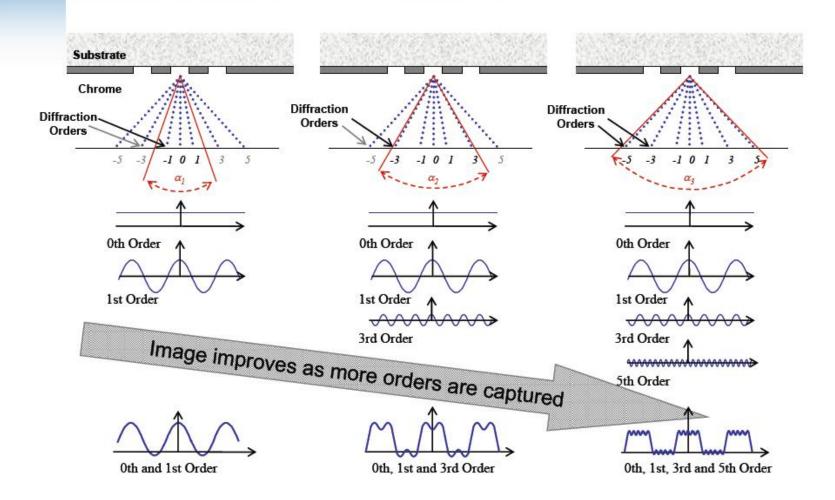

#### **Reminder on diffraction**

Diffraction : some intensity of light appears on masked area

•Fresnel Diffraction : near field ; sphericlal waves

•Fraunhoffer Diffraction: far field ; plane waves

•

#### Diffraction through a slit screen $\times$ 2a D Fraunhoffer $N_F = 0.5$ N<sub>F</sub>=1 $N_F = 0.1$ $N_F = 10$ 1. 1. $N_F = \frac{a^2}{\lambda D}$ 0. 0 0. 0. **Fresnel Number** -1. -1 -5 -2-

Fresnel

#### Optical lithography by proximity/contact

resolution limited by Fresnel diffraction:

$$R \approx \sqrt{\lambda(g+e)}$$

•Minimum gap= resist thickness

contact: •Substrate flatness •Resist damage •Mask damage •Masque 1:1

typically one can reach  $0.5\mu$ m in contact mode  $\lambda > 157$ nm for mask transparency (heating)

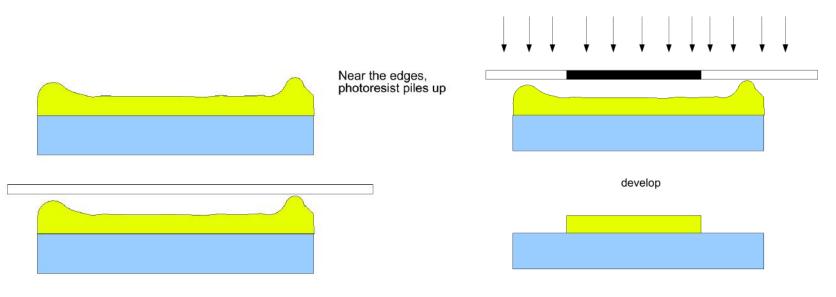

#### Problem with edges

The gap can be several tens of  $\mu m$

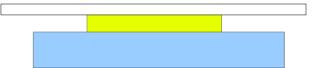

#### The various wavelengths from Hg lamp

Mask :

# Quartz plate of 4mm thickness (rigidity)

The pattern is realized by a selective etching of 80nm chromium

CONTRACTOR DE LA CONTRA

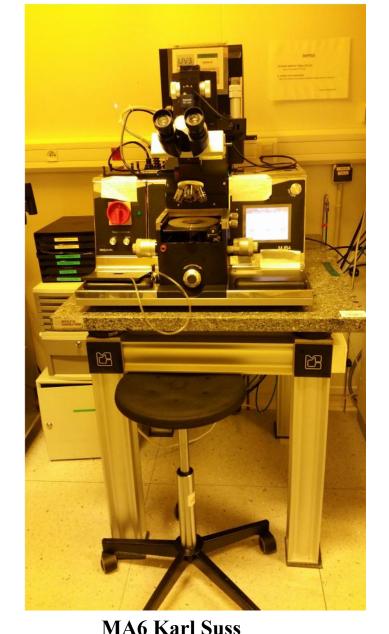

Simple and economical technique it is well developed in lab and R&D

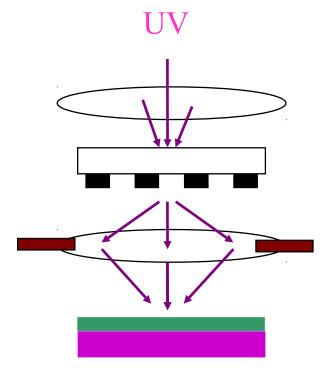

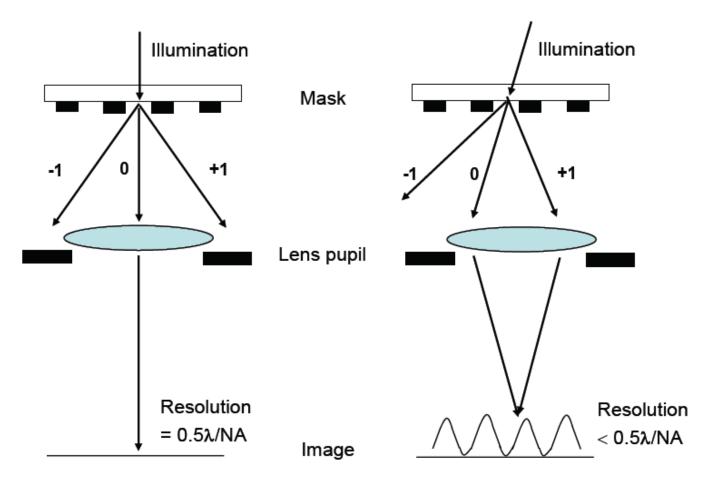

#### **Projection lithography**

A lens is used to project the image of the mask on the wafer

#### enlargment1:5 to 1:20

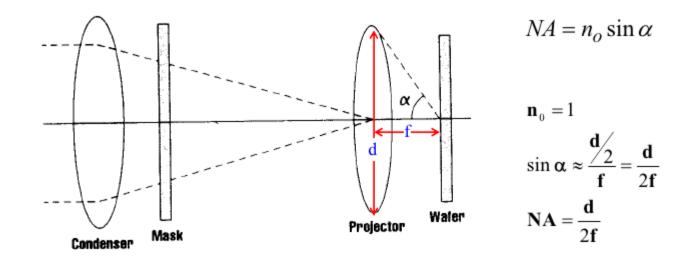

#### Numerical aperture

Numerical aperture is a measure of the capacity of the lens to capture light

$\alpha$  is the maximum angle that can be focused by the lens

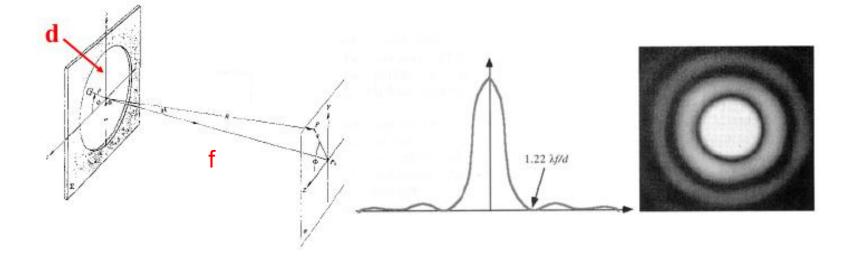

#### Fraunhoffer diffraction of an aperture

First minmum at x= 1.22  $\lambda f/d$

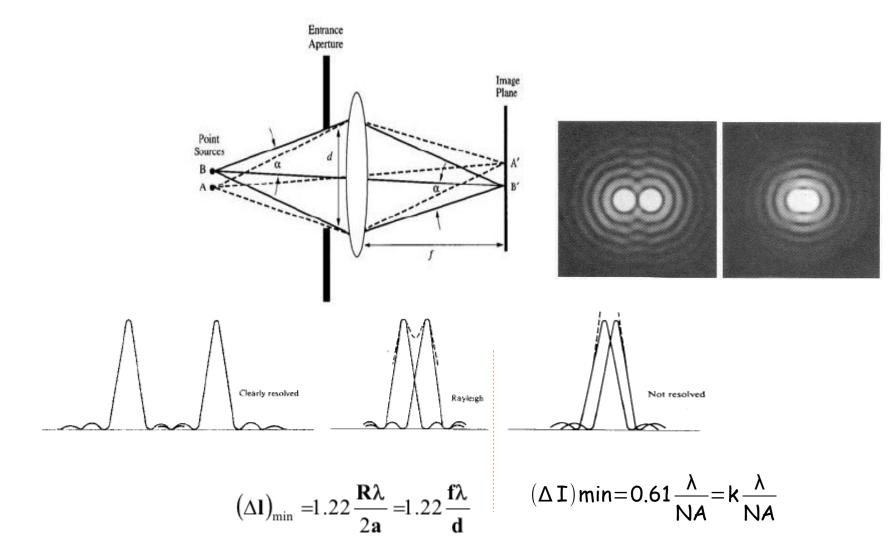

#### resolution

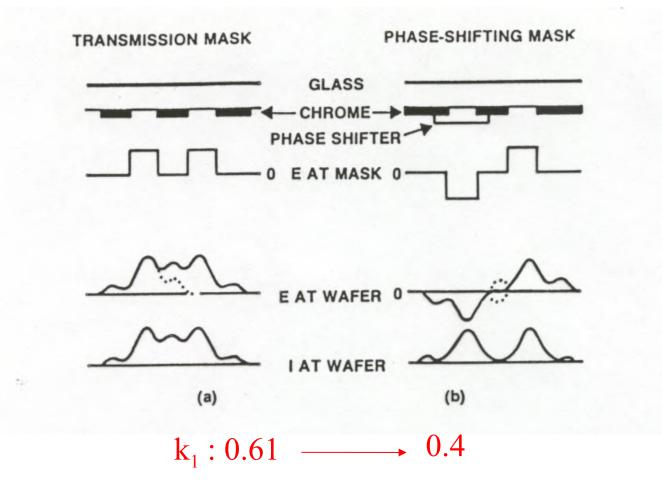

k is a technological parameter which is theoretically 0.61 but progresses will scaled it down

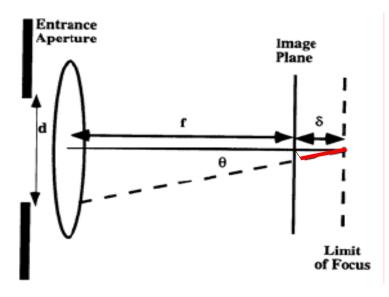

## Depth of focus

The depth of focus decrease when NA increases in conflict with the resolution.

Raleigh criteria for DOF : change in optical path between the zero order diffraction (on the optical axis) and the one by the edge of the aperture  $=\lambda/4$

$$\frac{\lambda}{4} = \delta - \delta \cos(\theta) = \delta(1 - \cos(\theta))$$

$$\cos(\theta) \approx 1 - (\theta)^{2}/2 \text{ small } \theta$$

$$\sin(\theta) \approx \theta$$

$$\frac{\lambda}{4} = \delta \frac{(NA)^{2}}{2} \qquad DOF = \frac{\lambda}{2NA^{2}}$$

Importance of the DOF: Flatness of the substrate Previous technological steps can give various heights

$DOF = k_2 \frac{\lambda}{NA^2}$

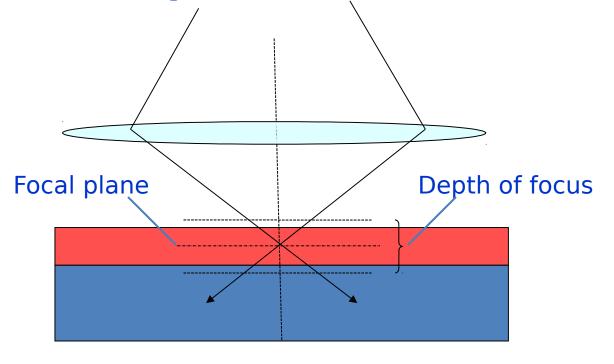

## Optimal focal plane in photolithography

- Light should be focused on the middle point of the resist layer.

- In IC, DOF is << 1 $\mu$ m, hard to focus if wafer is not super flat.

- People talks more of resolution, but actually DOF can often be a bigger problem than resolution.

- For example, a 248nm (KrF) exposure system with a NA = 0.6 would have a resolution of  $\approx 0.3 \mu m$  (k<sub>1</sub> = 0.75) and a DOF of only  $\approx \pm 0.35 \mu m$  (k<sub>2</sub> = 0.5).

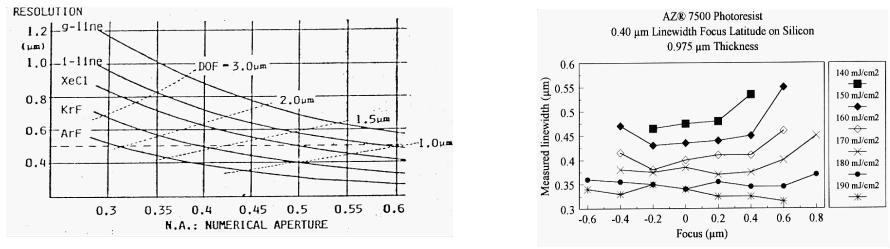

résolution, NA,  $\lambda$  and DOF

resolution vs focus and dose (i-line, NA=0.54)

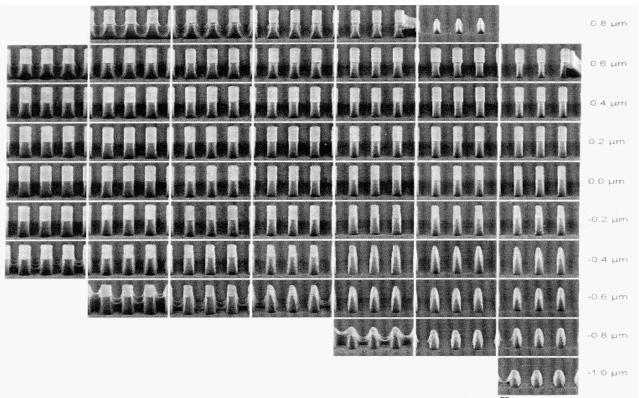

FIG. 1.31 Resist profiles for imaging at best focus and outside the depth of focus<sup>80</sup>.

DOF effect on exposure: profile in the resist upon varying the focus (y) and the dose (x)

The process latitude is strongly affected by the DOF

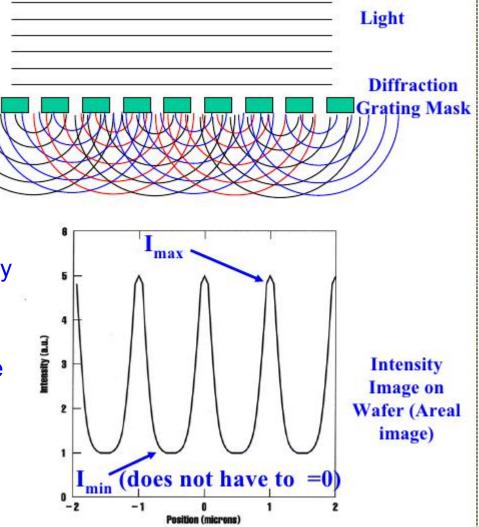

# Modulation Transfer Function (MTF)

One defines the ModulationTransfer Function :

$$MTF = \left[\frac{I_{\max} - I_{\min}}{I_{\max} + I_{\min}}\right]$$

MTF is a measure of the ability of the optical system to modulate the intensity of the light on the wafer

The smaller the period of the grating the bigger are diffraction effect and the MTF decreases. Usually MTF > 0.5 is preferred. It depends on  $\lambda$ , light source size (coherency), and optical system.

Importance of the resist contrast

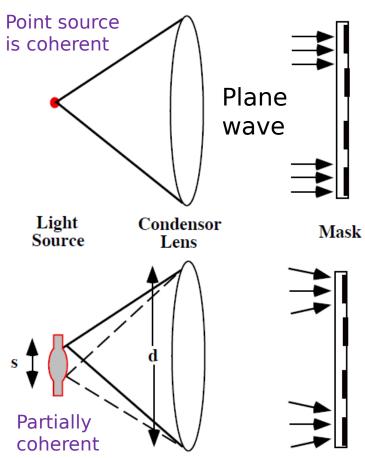

#### Spatial coherence of light source

- Coherent light will have a phase to space relationship.

- Incoherent light or light with only partial coherence will have wave-fronts that are only partially correlated.

- Spatial coherence S is an indication of the angular range of light waves incident on mask, or degree to which light from source are in phase.

- Small S is not always good (see next slide).

$$S = \frac{\text{source diameter}}{\text{aperture diameter}} = \frac{s}{d}$$

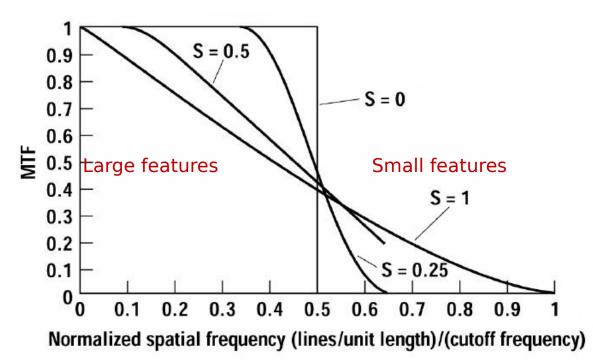

# MTF and spatial coherence

MTF vs. diffraction grating period on mask.

W = line width

X-axis of the plot: spatial frequency v=1/(2W), normalized to Rayleigh criterion cutoff frequency  $v_0=1/R=NA/(0.61\lambda)$ .

**2W** For a source with perfect spatial coherence S=0, MTF drops abruptly at Rayleigh criterion W=half pitch=R= $k_1\lambda/NA$ .

Large S is good for smaller features, but bad for larger ones.

Trade-off is made, and industry chooses S=0.5-0.7 as optimal.

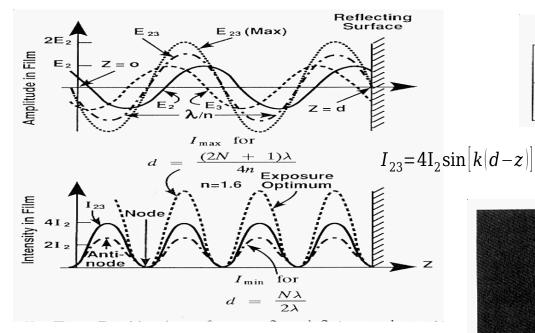

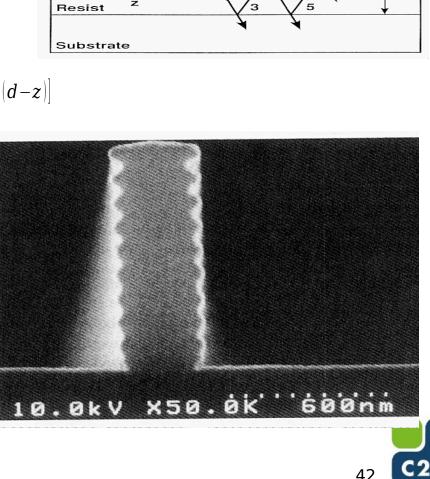

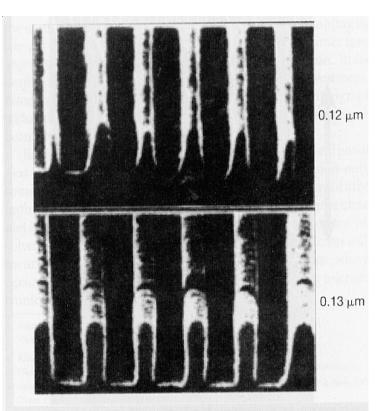

#### Interference effects in the resist

Constructive and destructive interference between incident and reflected light results in a periodic intensity distribution across the resist thickness.

Ambient

† d

#### Solutions:

Anti Reflecting Coating (ARC)

#### Optical lithographie

| Year | λ     | N.A. | resolution | k    |

|------|-------|------|------------|------|

| 1980 | 436nm | 0.28 | 1.25µm     | 0.8  |

| 1990 | 365nm | 0.48 | 0.5µm      | 0.65 |

| 1995 | 248nm | 0.5  | 0.3µm      | O.6  |

| 1999 | 248nm | 0.63 |            | 0.46 |

| 2004 | 193nm |      |            | 0.49 |

| 2010 | 193nm | 1.35 | 0.045µm    | 0.27 |

k<k<sub>Rayleigh</sub> by use of tricks: top imaging technique , phase shift mask, double exposure , off axis ... (RET)

### **Decreasing wavelength**

- When decreasing  $\lambda$ , one increases the absorption of materials.

- Below 193nm it is difficult to find a transparent material without absortion

- Absorption means temperature increase

- Temperature increase means dilatation

- In microelectronics 193nm is the limit for projection lithography

- A new option is EUV lithography with  $\lambda$ =13.5nm without lens

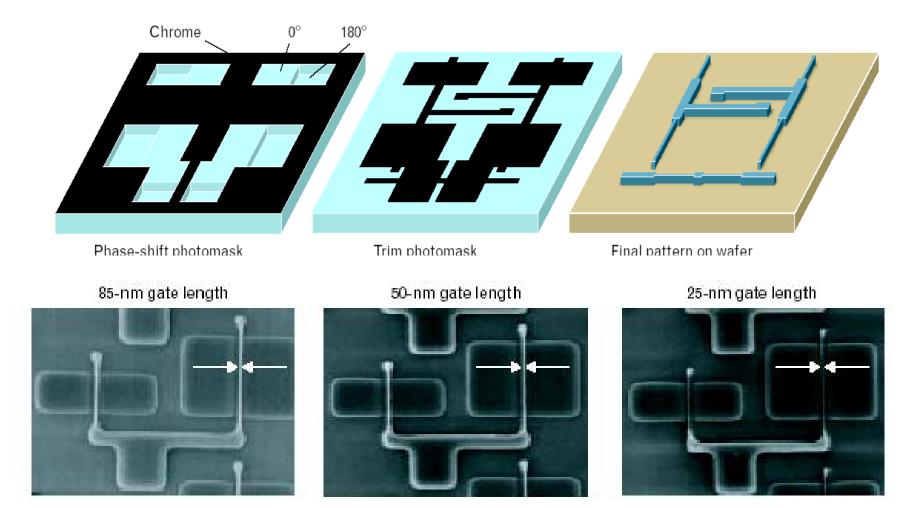

#### **RET** (Resolution Enhance Technologies)

Resolution enhancement technologies Modified illumination Light source Effective Quadle pole Conventional source Annular Phase shifting Condenser lens Mask π 0 Phase 0 0 π IIII Alternate Attenuated Mask Pupil filtering Pupil function **Projection lens** Phase distribution Aperture (pupil) Multiple exposure Multiple mask FLEX - Wafer Others Surfacing imaging Wafer stage thin resist film

**Figure 5** An example of resolution enhancement using phase-shifting technology. The exposure system uses a KrF excimer laser ( $\lambda = 0.248 \ \mu m$ ; NA = 0.55;  $\sigma = 0.3$ ) Structures having half the wavelength of the exposure light are clearly visible.

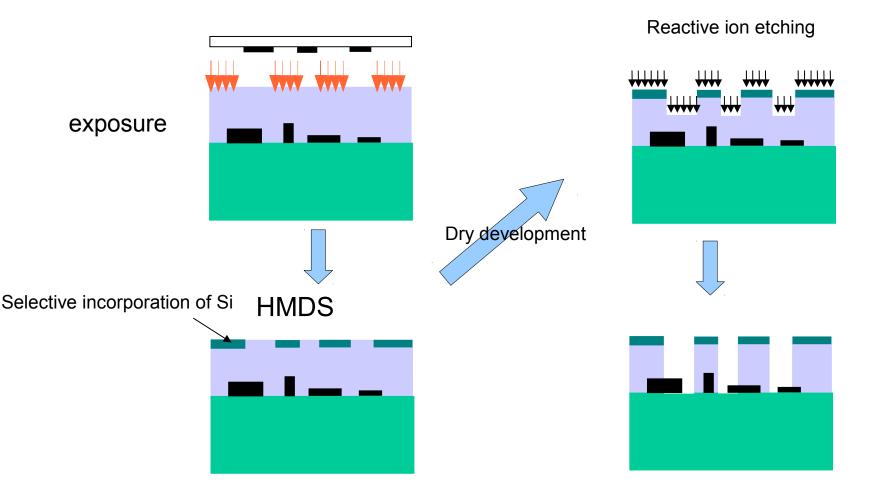

#### Top imaging technique

Not sensitive to DOF, interference in resist, planarisation

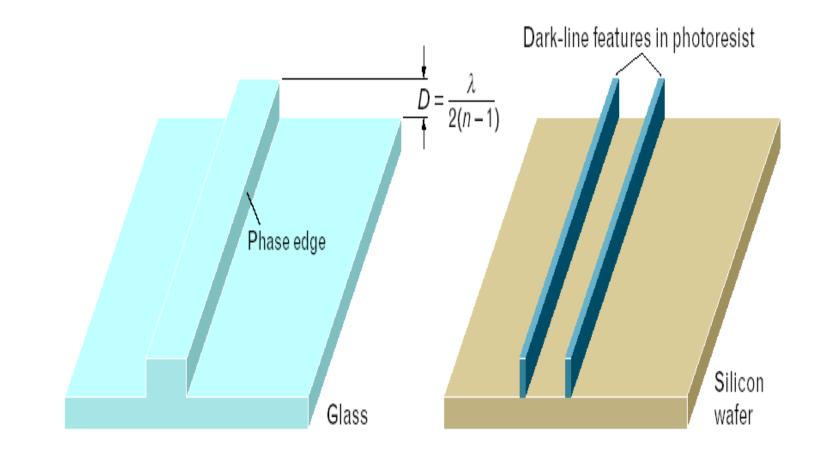

### Phase shifting mask

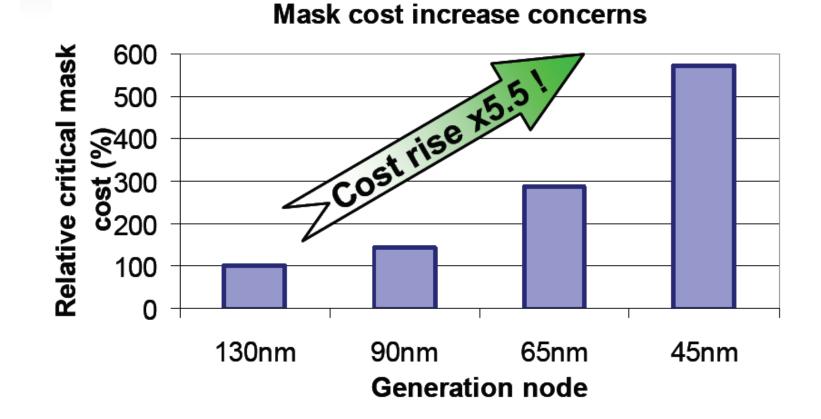

Mask more complex  $\rightarrow$  price!!

# Image Capture

© CEA 2006. Tous drolts réservés.

Toule reproduction totale ou partielle sur queique support que ce soit ou utilisation du contenu de ce document est interdite sans l'autoritation écrite préalable du CEA All rights reserved. Any reproduction in whole or in part on any medium or use of the information contained herein is prohibited without the prior written consent of CEA.

# Off axis illumination

This works well with regular gratings

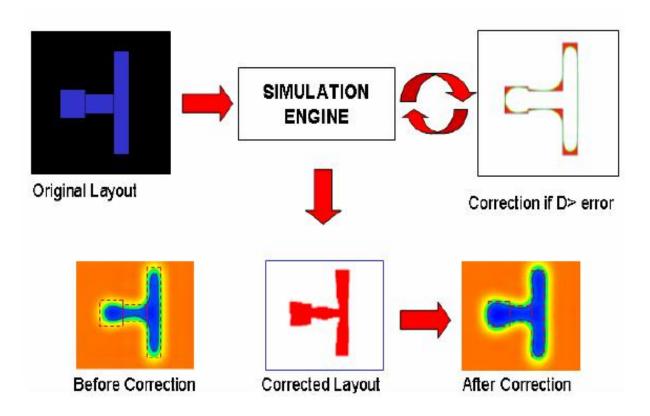

## **Optical Proximity Corrections**

Needs heavy computer programs to calculate diffraction effects and correct them

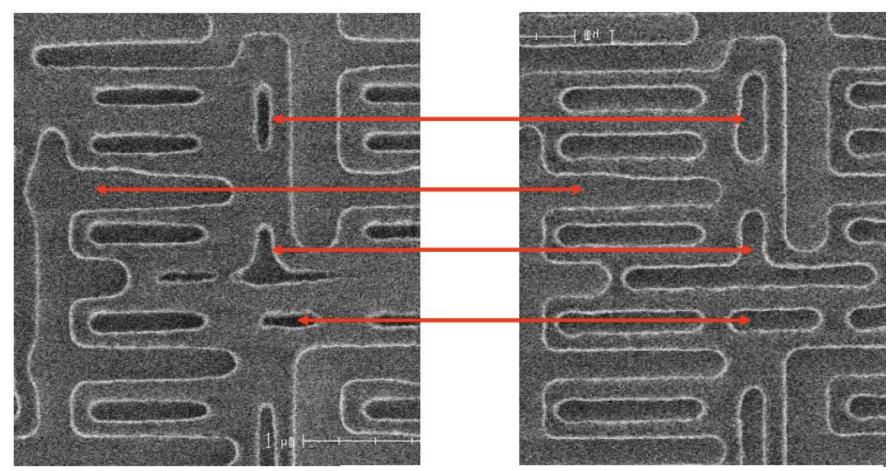

# Example

Without mask correction

With mask correction

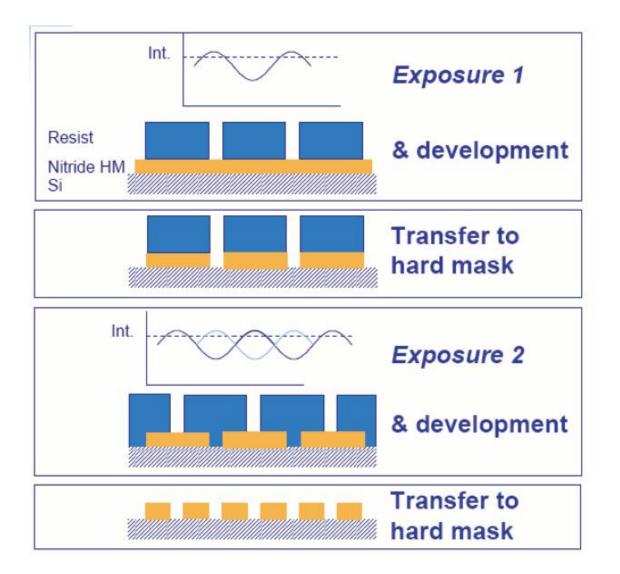

#### Double exposure

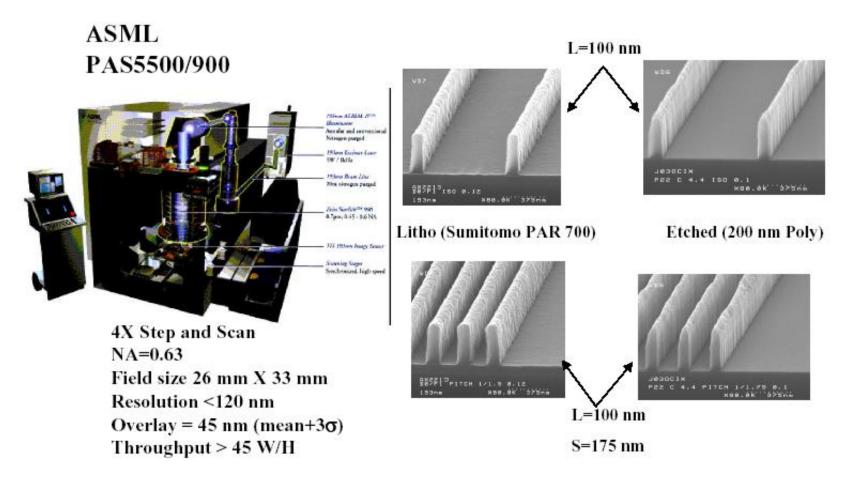

#### Stepper at 193nm

#### 10M€!

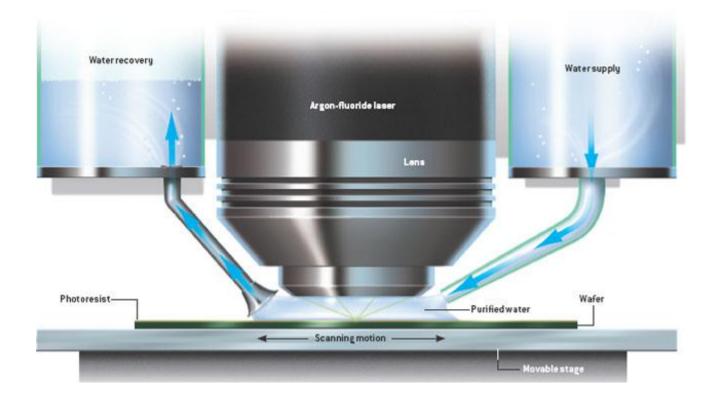

# **Immersion lithography**

NA=nsin $\theta$ , n of water 1.44, one can reach NA=1.35

# **Immersion lithography**

Water is very transparent to 193nm

Problems with water: Water may seem like an easy solution but its implementation presents some serious problems.

Water purification any impurity will introduce absorption Water/lens interface Water/resist interactions Defects o Backside contamination o Drying

How to keep water contained while in motion (speed of stepper 500cm/s!)

Other complex fluides with higher n are also used

This nowadays a common technique which is in strong competition with EUV

CINIS

57 C2N

|                    | 30                  | 300 mm line                                       |  |  |  |  |

|--------------------|---------------------|---------------------------------------------------|--|--|--|--|

| Front-en<br>(FEOL) |                     | F immersion lithography for 45 nm<br>CMOS process |  |  |  |  |

| Back-en<br>(BEOL)  | d Cu wiring us      | Cu wiring using Dual-Damascene                    |  |  |  |  |

|                    |                     |                                                   |  |  |  |  |

|                    |                     | 000000                                            |  |  |  |  |

|                    |                     | 000000                                            |  |  |  |  |

| 44.7 nm            | → ←<br>90 nm-pitch  | J20nm-pltch                                       |  |  |  |  |

|                    | 45 nm L & S Pattern | 120 nm-pitch/50 nm-CH                             |  |  |  |  |

#### Chromless mask

#### chromeless + double exposure

With  $\lambda$ =248nm et NA=0.6 soit un k1=0.06!

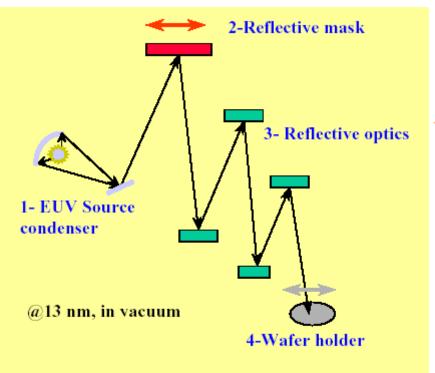

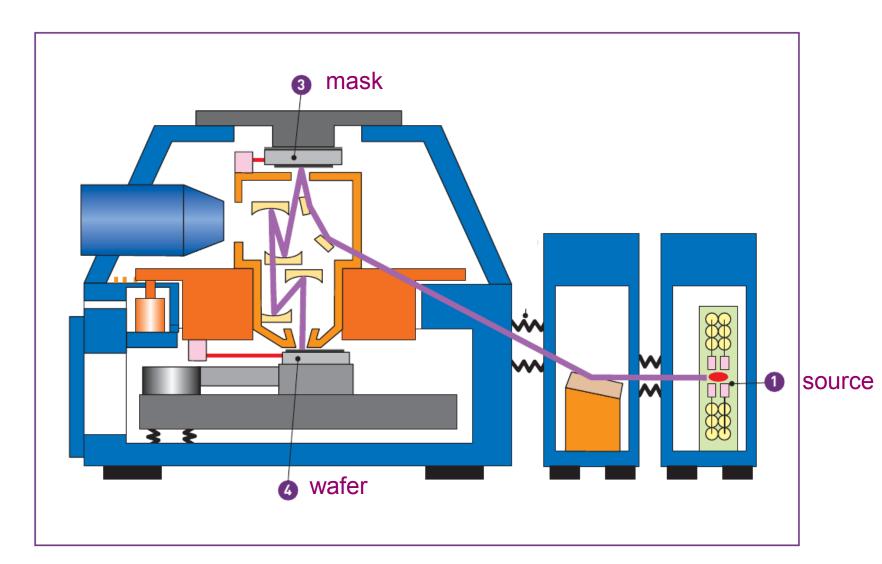

#### **EUV Lithography**

EUV are rapidely absorb in air The equipment needs to be in vacuum

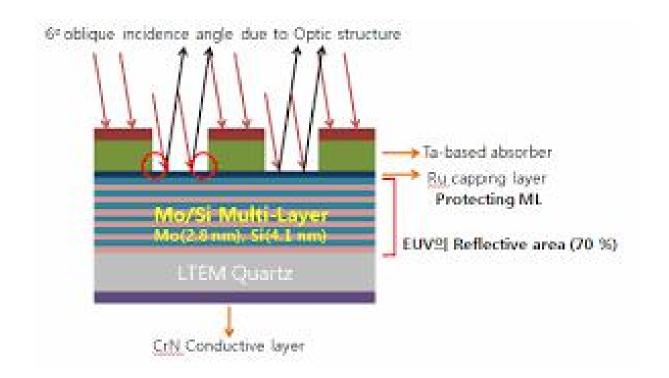

### EUV reflective mask

#### **EUV reflective optics : requirements**

• Aberrations

(For 70 nm CD)

- -> Surface figure : <0.2nm rms</p>

- Flare (parasitic light => contrast loss))

- -> Mid spatial frequency roughness : < 0.15nm rms

- Reflectivity loss

- -> High spatial frequency roughness : < 0.10nm rms</p>

- + Highest possible reflectivity

- + Aspherization

- + Graded multilayer thickness

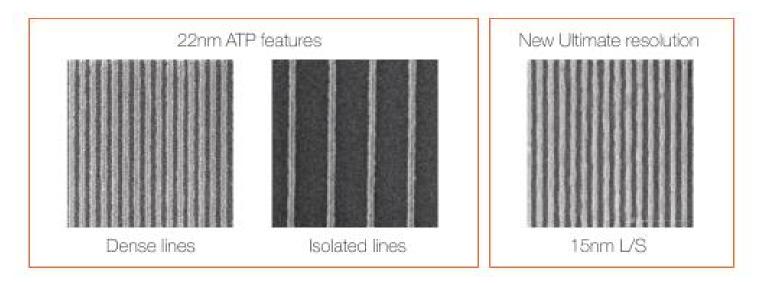

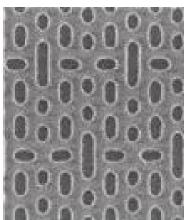

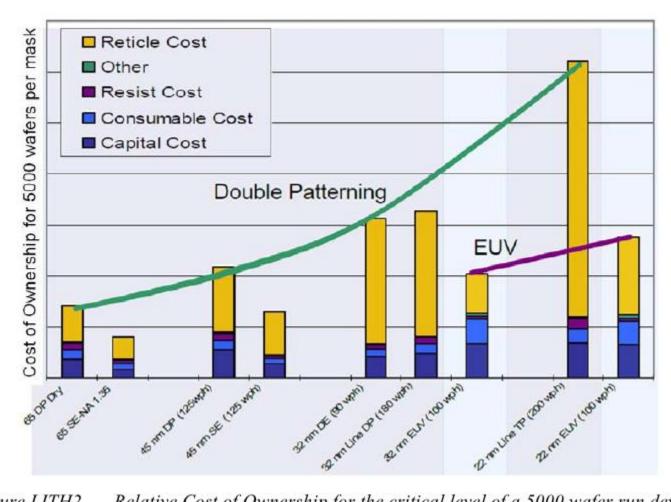

#### Big competition between EUV and immersion

EUV: 14 nm node Single exposure

EUV: 20 nm node Single exposure

UNIVERSITE

CNIS

ArFi: 20 nm node Double exposure

#### Costs

Figure LITH2 Relative Cost of Ownership for the critical level of a 5000 wafer run device

|                    |                    |                    | Number of          | Foundries with a C | utting Edge Logic F | ab              |                 |         |                 |       |

|--------------------|--------------------|--------------------|--------------------|--------------------|---------------------|-----------------|-----------------|---------|-----------------|-------|

| SilTerra           |                    |                    |                    |                    |                     |                 |                 |         |                 |       |

| X-FAB              |                    |                    |                    |                    |                     |                 |                 |         |                 |       |

| Dongbu HiTek       |                    |                    |                    |                    |                     |                 |                 |         |                 |       |

| ADI                | ADI                |                    |                    |                    |                     |                 |                 |         |                 |       |

| Atmel              | Atmel              |                    |                    |                    |                     |                 |                 |         |                 |       |

| Rohm               | Rohm               |                    |                    |                    |                     |                 |                 |         |                 |       |

| Sanyo              | Sanyo              |                    |                    |                    |                     |                 |                 |         |                 |       |

| Mitsubishi         | Mitsubishi         |                    |                    |                    |                     |                 |                 |         |                 |       |

| ON                 | ON                 |                    |                    |                    |                     |                 |                 |         |                 |       |

| Hitachi            | Hitachi            |                    |                    |                    |                     |                 |                 |         |                 |       |

| Cypress            | Cypress            | Cypress            |                    |                    |                     |                 |                 |         |                 |       |

| Sony               | Sony               | Sony               |                    |                    |                     |                 |                 |         |                 |       |

| Infineon           | Infineon           | Infineon           |                    |                    |                     |                 |                 |         |                 |       |

| Sharp              | Sharp              | Sharp              |                    |                    |                     |                 |                 |         |                 |       |

| Freescale          | Freescale          | Freescale          |                    |                    |                     |                 |                 |         |                 |       |

| Renesas (NEC)      |                     |                 |                 |         |                 |       |

| SMIC               | SMIC               | SMIC               | SMIC               | SMIC               |                     |                 |                 |         |                 |       |

| Toshiba            | Toshiba            | Toshiba            | Toshiba            | Toshiba            |                     |                 |                 |         |                 |       |

| Fujitsu            | Fujitsu            | Fujitsu            | Fujitsu            | Fujitsu            |                     |                 |                 |         |                 |       |

| ті                 | ті                 | ті                 | ті                 | ті                 |                     |                 |                 |         |                 |       |

| Panasonic          | Panasonic          | Panasonic          | Panasonic          | Panasonic          | Panasonic           |                 |                 |         |                 |       |

| UMC                | UMC                | UMC                | UMC                | UMC                | UMC                 |                 |                 |         |                 |       |

| STMicroelectronics | STMicroelectronics | STMicroelectronics | STMicroelectronics | STMicroelectronics | STMicroelectronics  |                 |                 |         |                 |       |

| IBM                | IBM                | IBM                | IBM                | IBM                | IBM                 | IBM             |                 |         |                 |       |

| AMD                | AMD                | AMD                | GlobalFoundries    | GlobalFoundries    | GlobalFoundries     | GlobalFoundries | GlobalFoundries |         | GlobalFoundries |       |

| Samsung            | Samsung            | Samsung            | Samsung            | Samsung            | Samsung             | Samsung         | Samsung         | Samsung | Samsung         |       |

| TSMC               | TSMC               | TSMC               | TSMC               | TSMC               | TSMC                | TSMC            | TSMC            | TSMC    | TSMC            |       |

| Intel              | Intel              | Intel              | Intel              | Intel              | Intel               | Intel           | Intel           | Intel   | Intel           | Futur |

| 180 nm             | 130 nm             | 90 nm              | 65 nm              | 45 nm/40 nm        | 32 nm/28 nm         | 22 nm/20 nm     | 16 nm/14 nm     | 10 nm   | 7 nm            | 5 nm  |

>193nm immersion with DE/DP allows to reach 14nm node

- Below 14nm EUVL seems the best candidate

- What about the 7nm node and below ?

People are also thinking to surface plasmon modes or evanescent modes lithography.....